# **IBIS Model Validation Review**

Lance Wang <u>Iwang@iometh.com</u> IBIS Asian Summit 2012 Nov. 16, 2012 Yokohama, Japan

# Outlines

- Motivation

- History

- Method Review

- Common Mistakes

- Conclusion

### **Motivation**

- Why is model validation a MUST?

- Models are artificial representations of the real devices. This applies to all the models including our SI simulation models

- System design engineers need the validated models to analyze their High-Speed system designs through simulations

- "Garbage in, Garbage out" is true for all the simulations

- Proper IBIS model validation method is required

- IBIS is a behavioral model which has no way to verify internal structures or monitor internal signals

- Common mistakes for IBIS validation and correction methods

Note: this presentation is focusing on "traditional" IBIS buffer model validation methods only.

# History

- 1997 the IBIS Accuracy Subcommittee (IAS) was established

- 1998 IAS releases their initial version of the IBIS Accuracy Specification, which later becomes the I/O Buffer Accuracy Handbook.

- 2007 the IBIS Quality Task Group (IQTG) was formed

- It is still ON in the regular teleconference basis

- Several IBIS Quality Specifications have been released as the IBIS Standard Specification documents

- A Quality Checklist also has been release from IQTG

- In the past few years, many system companies start to ask their device vendors to have their specific IBIS model quality control documents filled before the devices are used in their high-speed designs

#### Method Review

- IBIS Validation Goal

- Correlate IBIS model simulation results with the desired Golden sources (measurements and simulations) for specific test loads

- Commonly Used Correlation/Comparison Methods

- From IQTG

- Quality Checklist

- From the Accuracy Handbook

- Curve Overlay Metric

- Curve Envelop Metric

- From Xilinx and Huawei

- Threshold based Metric

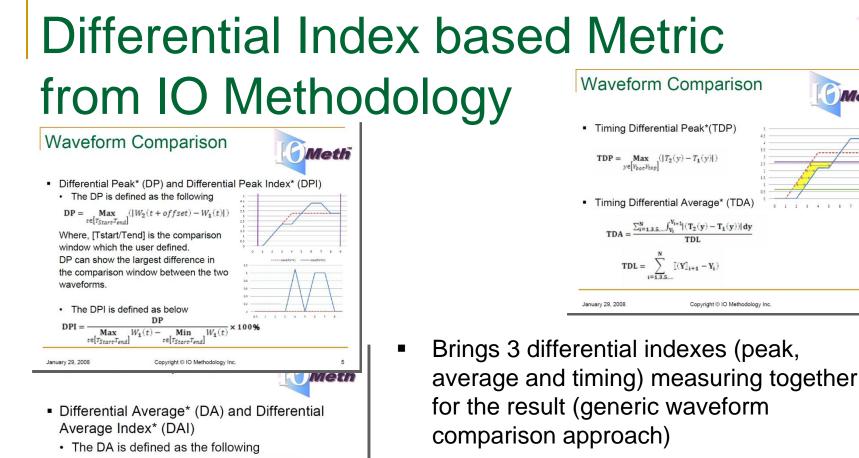

- From IO Methodology

- Differential Index based Metric

# Quality Checklist from IQTG

- Great start! A lot of good suggestions

- Simply follow the list for the check items

- Too many items asking for "reasonable" and "visual" checking

- Not easy to implement by using a computer program

- Incomplete especially for correlations

| 10 <b>  IC</b>      | 2    | See IBIS Quality Spec | ification fo   | r complete descriptions of the checks.                                                          |           |          |  |

|---------------------|------|-----------------------|----------------|-------------------------------------------------------------------------------------------------|-----------|----------|--|

| 11 <b>  IC</b>      | 2    |                       |                |                                                                                                 |           |          |  |

| 12 <b>  IC</b>      | 2    |                       |                |                                                                                                 |           |          |  |

| 13 <b> IC</b>       | 2    |                       |                |                                                                                                 |           |          |  |

| 14 10               | 2    | IQ Spec Reference     | IQ LEVEL       | Description                                                                                     | PASS/FAIL | Comments |  |

| 15  10              | 2    | 5.1.1                 | LEVEL 2        | [Model] parameters have correct typ/min/max order                                               |           |          |  |

| 16  IC              | 2    | 5.1.2                 | LEVEL 2        | [Model] C_comp is reasonable                                                                    |           | -        |  |

| 17  IC              | 2    | 5.1.3                 | LEVEL 2        | [Temperature Range] is reasonable                                                               |           | Î        |  |

| 18 10               | 2    | 5.1.4                 | LEVEL 2        | [Voltage Range] or [* Reference] is reasonable                                                  |           |          |  |

| 19 <b>  IC</b>      | 2    | 5.2.1                 | LEVEL 3        | [Model] Vinl and Vinh reasonable                                                                |           |          |  |

| 20 10               | 2    | 5.2.2                 | LEVEL 3        | [Model Spec] Vinl and Vinh reasonable                                                           |           |          |  |

| 21 10               | 2    | 5.2.3                 | LEVEL 3        | [Model Spec] Vinl+/- and Vinh+/- complete and reasonable                                        |           |          |  |

| 22 10               | 2    | 5.2.5                 | LEVEL 2        | [Model Spec] S_Overshoot subparameters complete and match data sheet                            |           |          |  |

| 23 10               | 2    | 5.2.6                 | LEVEL 2        | [Model Spec] S_Overshoot subparameters track typ/min/max                                        |           |          |  |

| 24 10               | 2    | 5.2.7                 | LEVEL 2        | [Model Spec] D_Overshoot_* subparameters complete and match data sheet                          |           |          |  |

| 25 10               | ב    | 5.2.8                 | LEVEL 2        | [Model Spec] D_Overshoot_* subparameters track typ/min/max                                      |           |          |  |

| 26 10               | 2    | 5.2.9                 | LEVEL 3        | [Receiver Thresholds] Vth present and matches data sheet, if needed                             |           |          |  |

| 27 <b>  IC</b>      | 2    | 5.2.10                | LEVEL 3        | [Receiver Thresholds] Vth_min and Vth_max present and match data sheet, if needed               |           |          |  |

| 28 10               | 2    | 5.2.11                | LEVEL 3        | [Receiver Thresholds] Vinh_ac, Vinl_ac present and match data sheet, if needed                  |           |          |  |

| 29 10               | 2    | 5.2.12                | LEVEL 3        | [Receiver Thresholds] Vinh_dc, Vinl_dc present and match data sheet, if needed                  |           |          |  |

| 30 <b>  IC</b>      | 2    | 5.2.13                | LEVEL 3        | [Receiver Thresholds] Tslew_ac/Tdiffslew_ac present and match data sheet, if needed             |           |          |  |

| 31  IC              | 2    | 5.2.14                | LEVEL 3        | [Receiver Thresholds] Threshold_sensitivity and Ext_ref present and match data sheet, if needed |           |          |  |

| 32 <b>  IC</b>      | ב    | 5.3.1                 | LEVEL 2        | I-V tables have correct typ/min/max order                                                       |           |          |  |

| 33 <b>  IC</b>      | 2    | 5.3.2                 | LEVEL 2        | [Pullup] voltage sweep range is correct                                                         |           |          |  |

| 34 <mark> IQ</mark> |      | 5.3.3                 | LEVEL 2        | [Pulldown] voltage sweep range is correct                                                       |           |          |  |

| 35 10               | 2    | 5.3.4                 | LEVEL 2        | [POWER Clamp] voltage sweep range is correct                                                    |           |          |  |

| 36 10               | 2    | 5.3.5                 | LEVEL 2        | [GND Clamp] voltage sweep range is correct                                                      |           |          |  |

| 37 <b>  IC</b>      | 2    | 5.3.6                 | LEVEL 2        | I-V tables do not exhibit stair-stepping                                                        |           |          |  |

| 38 10               |      |                       | LEVEL 2        | Combined I-V tables are monotonic                                                               |           |          |  |

| 4 4 🕨               | ▶I S | ummary / components   | () <b>mode</b> | is()                                                                                            | in        |          |  |

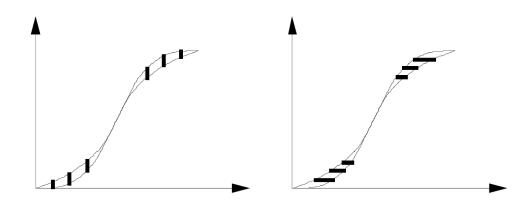

# **Curve Overlay Metric**

- Relatively simply method

- Easy to implement by using a computer program

- Large error occurs when most points are not perfectly aligned up even though visual check seems to be good

- Does not count the error due to waveform shifting

- Not a great reference for automation purposes

#### 4.3 Curve Overlay Metric

The Curve Overlay Metric applies to cases in which the measured and simulated data should theoretically lie directly on top of each other. For example, a structural simulation of a 50  $\Omega$  load and a behavioral simulation of the same load should theoretically yield identical results. Another example is the measurement of a known-typical sample component and a structural simulation of the same network under identical process-voltage-temperature conditions. The Curve Overlay Metric measures how well the two curves or waveforms match each other by summing the absolute value of the x-axis (or y-axis) differences between the two data points, weighing the sum against the range of data points along that axis, and dividing by the number of data points.

$$FOM = 100 \cdot \left[ 1 - \frac{\sum_{i=1}^{N} |X_i(golden) - X_i(DUT)|}{\Delta X \cdot N} \right]$$

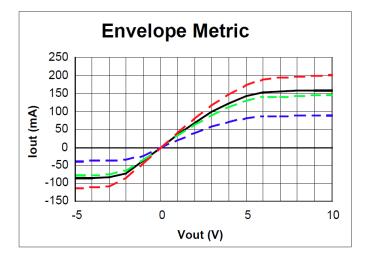

### **Curve Envelope Metric**

#### 4.4 Curve Envelope Metric

The Curve Overlay Metric applies to cases in which the measured data are, in theory, bounded by two curves (or waveforms) that represent process-voltage-temperature extremes. In general, this metric is useful when the processing conditions of the sample component are unknown. The Curve Overlay Metric returns a yes/no value depending on whether or not every one of the data points falls within the envelope boundaries defined by the min and max curves. The plot below demonstrates a lab pull-down curve (solid line) that is slightly stronger than the typical curve (middle dashed line) and lies well within the (outer dashed lines).

- Good to be used for measurement correlation cases

- Applies a good estimate for unknown/hard\_to\_ control operation conditions

- No result that indicates how accurate the model is

The Curve Envelope Metric presents a difficulty in the case of unterminated transmission line loads. Because these waveforms overshoot normal logic levels and ring back, the min and max waveforms intersect each other and do not define an envelope. Therefore, the Curve Envelope Metric may not be applied to the Open Transmission Line load or the Transmission Line and Receiver load.

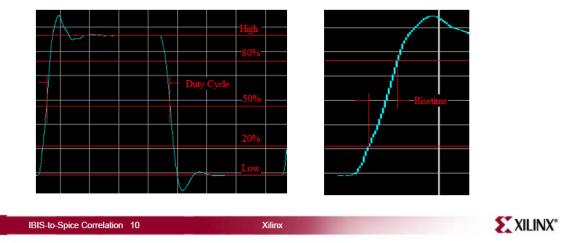

# Threshold based Metric from Xilinx

- Uses 5 of the most important thresholds to measure the correlation result

- Simple and easy to use a computer program for the results

- Ignores some transition effects

- Difficult to be used for some abnormal waveform correlations

#### **5 Metrics Defined**

- We propose the following 5 metrics/features for waveform comparison:

- high level, low level, rise time, fall time, and duty cycle

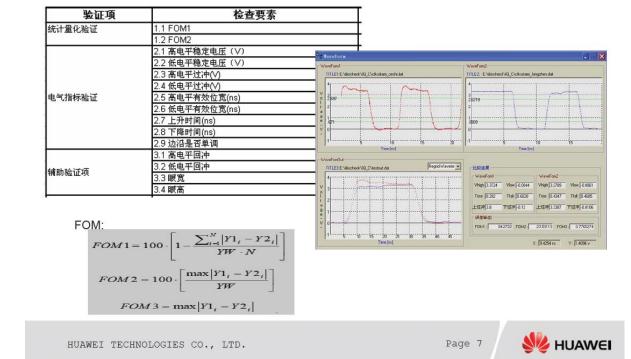

# Threshold based Metric from

Huawei

- Uses more thresholds to measure the correlation result including overshoots, monotonicity and eye measurements, etc. Plus FOM and customized FOMs

- Getting more difficult to use a computer program for the results but kind of manageable

- Still difficult to be used for some abnormal waveform correlations

- $$\begin{split} DA = & \frac{\sum_{i=1,3,5,\dots}^{N} \int_{T_{i}}^{T_{i}+1} |(W_{2}(t+\textit{offset})-W_{1}(t))| \, dt}{DL} \\ & \\ DL = & \sum_{i=1,3,5,\dots}^{N} [(T]_{i+1}-T_{i})] \end{split}$$

- The DAI is defined as below

- Close to human visual predictions

- No dependency for threshold settings

- Works fine even for abnormal waveforms

- Must use a computer program to calculate

Meth

# **Common Mistakes**

- Syntax Check

- IBIS Golden Parser is a good first-pass tool for "legal" IBIS syntax check

- Most simulators will stop if your IBIS file contains syntax errors

- No errors and warnings doesn't mean it is a good IBIS model for simulations

- With warning messages, the IBIS model might still produce accurate results against golden sources

- Test Circuit

- Proper test circuit is important to get meaningful validation results

- Your IBIS model might not be operable for certain conditions. It might heavily depend on your extraction conditions

- Use application level test circuit for your correlations

# Common Mistakes (continued)

- I-V / V-T Curves

- Individual I-V might not be within your expectations. Need to check the combined curves instead

- IBIS Spec only accepts 100 data points for I-V curves

- A number of system vendors asked for 1000 I-V points

- Do not always use/ask 2 sets of V-T curves with 50 ohm + V\_fixture=VCC/GND

- Some buffers are only working properly for high-impedance load

- Some buffers will produce a straight line for V\_fixture=VCC or GND. e.g. OPEN type buffers

- For some differential buffers, you might have to set

V\_fixture=Common\_mode\_voltage

- Be careful about I-V / V-T mismatch error/warning

- Most of the time, this mismatch indicates your IBIS extraction settings are improper or inconsistent

- Beware of fixing

- > Don't fix it if it is not just a numerical error. It might have to be extracted again

## Conclusion

- Validation is better to be done by IBIS model vendors

- Comparison methods vary. Use them wisely to fit your buffer model needs.

- IBIS users should ask the vendor for reasonable validation reports and/or test bench files

- I/O buffers vary. Be sure the contents you asked for are reasonable

- The different simulators could give out different IBIS simulation results

http://www.iometh.com